# Analysis, Modeling and Optimization of Execution Time and Energy for Parallel Programs

## PhD thesis in Computer Science

by

## Philipp Gschwandtner

submitted to the Faculty of Mathematics, Computer Science and Physics of the University of Innsbruck

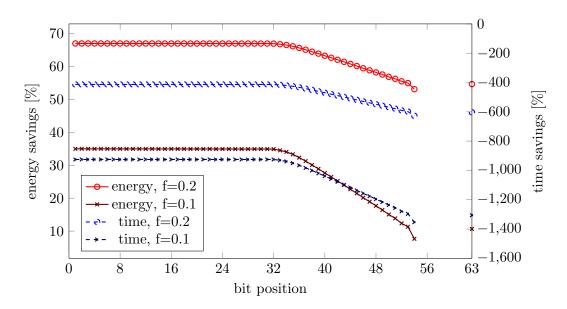

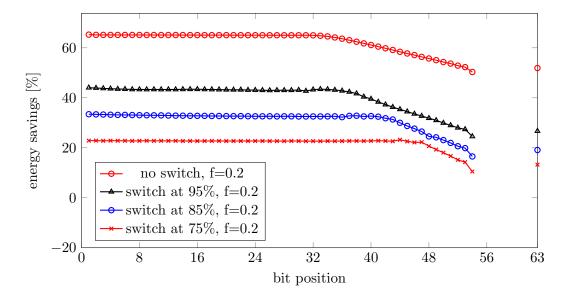

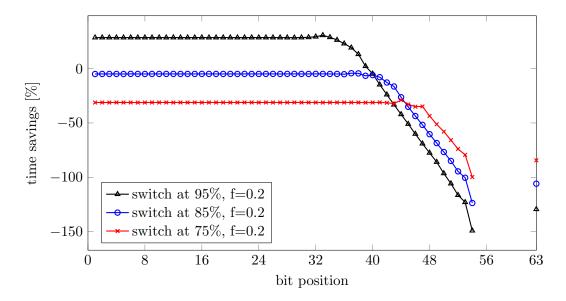

> in partial fulfillment of the requirements for the degree of doctor of philosophy

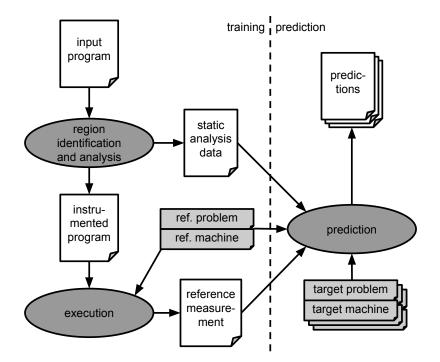

advisor: Prof. Dr. Thomas Fahringer, Institute of Computer Science

Innsbruck, February 20, 2017

#### Certificate of Authorship and Originality

I certify that the work in this thesis has not previously been submitted for a degree nor has it been submitted as part of requirements for a degree except as fully acknowledged within the text.

I also certify that the thesis has been written by me. Any help that I have received in my research work and the preparation of the thesis itself has been acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis.

Philipp Gschwandtner, Innsbruck, February 20, 2017

#### Abstract

Traditionally, high performance computing (HPC) considered execution time as the most important objective for optimizing parallel programs. However, the power wall and also the subsequent rise of multi- and manycore designs forced the scientific community and industry to shift their focus towards additional concerns, such as energy consumption, power consumption or thermal budgets. Nowadays, these concerns often pose the limiting factor when designing faster hardware or optimizing software.

Contrary to much related work in this field, targeting hardware design, scheduling, or resource management, the research presented in this thesis investigates several non-functional parameters (including execution time and energy consumption) from a compiler perspective. Employing the unique capabilities of a compiler, it tackles three research use cases. First, we examine the conflicting nature of three non-functional parameters in the context of multi-objective auto-tuning. Second, we investigate the concept of code significance and how it can be leveraged to drive program execution on unreliable hardware in order to reduce energy consumption. Third, we discuss the benefits of compiler-assisted predictive models with regard to overhead reduction.

To investigate these open research problems, a hardware and software model suitable for compilers is established in this doctoral thesis, enriched with key properties with respect to the aforementioned tasks. Implemented and integrated into the Insieme compiler and runtime system framework, it supports the automatic identification of target code regions, enables the specification of key properties, extensible by additional concepts such as user-defined metrics.

#### Acknowledgements

Foremost, I would like to express my sincere gratitude to my advisor Prof. Dr. Thomas Fahringer for his continuous support of my Ph.D study and research, for his patience, motivation, knowledge and experience. His guidance helped me in all the time of research and writing of this thesis. Additionally, I would also like to thank my second supervisor Prof. Dr. Sabine Schindler for her support and the opportunity to participate in the Doctoral School Computational Interdisciplinary Modelling, the external reviewers for their valued perspective on my work, and the rest of the thesis committee.

I also thank Dr. Juan Durillo for his highly valued assistance in major parts of my research, and Dr. Radu Prodan for his insightful comments and experience. Additionally, I would like to express my gratitude to both Dr. Dimitrios Nikolopoulos and Dr. Bernd Mohr for their highly esteemed guidance, support, and access to research facilities abroad they helped me broaden my horizon in science, work, and also culture.

My sincere thanks also go to all my fellow students and colleagues, most notably Ferdinando Alessi, Luis Ayuso, Alex Hirsch, Bernhard Höckner, Matthias Janetschek, Herbert Jordan PhD, Klaus Kofler, Stefan Moosbrugger, and Peter Zangerl. They all contributed to our common projects and goals, and we shared a great many productive and entertaining discussions about work-related topics and also virtually everything else that came to mind during our time in the office. I particularly thank Dr. Peter Thoman for our fruitful and fun discussions in the office, my car, and on the trail, and for his and Herbert's demands for high-quality work.

Finally, I would like to thank both my parents, my sister, and Lisa for supporting me in all my endeavors. They encouraged me to pursue my dreams throughout all these years, and continue to do so.

# Contents

| Ce       | Certificate of Authorship          |        |                                                          |           |  |  |  |  |

|----------|------------------------------------|--------|----------------------------------------------------------|-----------|--|--|--|--|

| A        | Abstract v<br>Acknowledgements vii |        |                                                          |           |  |  |  |  |

| A        |                                    |        |                                                          |           |  |  |  |  |

| Ta       | able o                             | of Con | tents                                                    | ix        |  |  |  |  |

| 1        | Intr                               | oduct  | ion                                                      | 1         |  |  |  |  |

|          | 1.1                                | Motiv  | ation                                                    | 1         |  |  |  |  |

|          | 1.2                                | State  | of the Art                                               | 2         |  |  |  |  |

|          |                                    | 1.2.1  | Multi-objective Auto-Tuning                              | 2         |  |  |  |  |

|          |                                    | 1.2.2  | Significance-driven Optimization of Code Execution       | 3         |  |  |  |  |

|          |                                    | 1.2.3  | Compiler-assisted Execution Time and Energy Modeling     | 4         |  |  |  |  |

|          | 1.3                                | Organ  | ization                                                  | 5         |  |  |  |  |

| <b>2</b> | Mo                                 | del    |                                                          | 7         |  |  |  |  |

|          | 2.1                                | Hardv  | vare Model                                               | 7         |  |  |  |  |

|          |                                    | 2.1.1  | Physics Background                                       | 7         |  |  |  |  |

|          |                                    | 2.1.2  | Topology                                                 | 9         |  |  |  |  |

|          |                                    | 2.1.3  | Non-functional Hardware Properties                       | 12        |  |  |  |  |

|          | 2.2                                | Softwa | are Model                                                | 20        |  |  |  |  |

|          |                                    | 2.2.1  | Software Structure                                       | 20        |  |  |  |  |

|          |                                    | 2.2.2  | Non-functional Software Properties                       | 22        |  |  |  |  |

|          | 2.3                                | Summ   | nary                                                     | 24        |  |  |  |  |

| 3        | Insi                               | eme N  | leasurement Framework                                    | <b>25</b> |  |  |  |  |

|          | 3.1                                | Comp   | iler Component                                           | 26        |  |  |  |  |

|          |                                    | 3.1.1  | Overview                                                 | 26        |  |  |  |  |

|          |                                    | 3.1.2  | Region Specification, Identification and Instrumentation | 27        |  |  |  |  |

## CONTENTS

|   |                                                       | 3.1.3             | Measurement Framework                                              | 28 |  |  |  |  |

|---|-------------------------------------------------------|-------------------|--------------------------------------------------------------------|----|--|--|--|--|

|   | 3.2                                                   | Runtime Component |                                                                    |    |  |  |  |  |

|   |                                                       | 3.2.1             | Overview                                                           | 30 |  |  |  |  |

|   |                                                       | 3.2.2             | Measurement Framework                                              | 30 |  |  |  |  |

|   |                                                       | 3.2.3             | Platform-specific Features                                         | 34 |  |  |  |  |

|   |                                                       | 3.2.4             | Control features                                                   | 36 |  |  |  |  |

|   | 3.3                                                   | Addit             | ional Research                                                     | 36 |  |  |  |  |

|   | 3.4                                                   | Summ              | nary                                                               | 36 |  |  |  |  |

| 4 | Multi-Objective Auto-Tuning 39                        |                   |                                                                    |    |  |  |  |  |

|   | 4.1                                                   | Introd            | luction                                                            | 39 |  |  |  |  |

|   | 4.2                                                   | Relate            | ed Work                                                            | 40 |  |  |  |  |

|   | 4.3                                                   | Insien            | ne Compiler                                                        | 42 |  |  |  |  |

|   |                                                       | 4.3.1             | Auto-Tuning Infrastructure                                         | 42 |  |  |  |  |

|   |                                                       | 4.3.2             | Optimizers                                                         | 43 |  |  |  |  |

|   | 4.4                                                   | Exper             | iment Design                                                       | 45 |  |  |  |  |

|   |                                                       | 4.4.1             | Objectives                                                         | 45 |  |  |  |  |

|   |                                                       | 4.4.2             | Benchmarks and Target Platform                                     | 46 |  |  |  |  |

|   |                                                       | 4.4.3             | Configuration of the Optimizers                                    | 47 |  |  |  |  |

|   |                                                       | 4.4.4             | Comparison Criteria                                                | 48 |  |  |  |  |

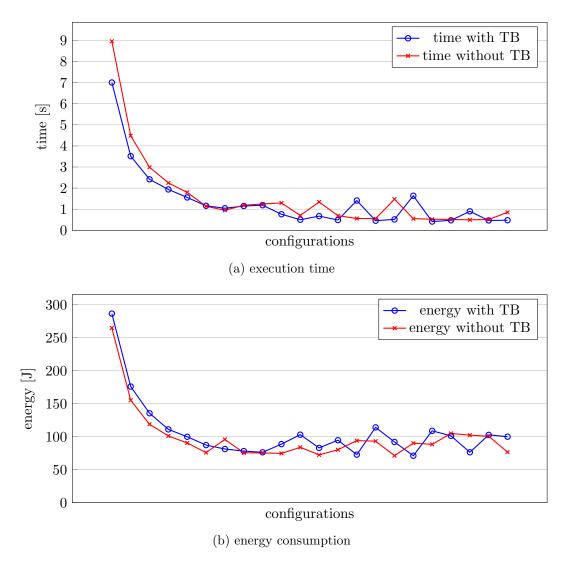

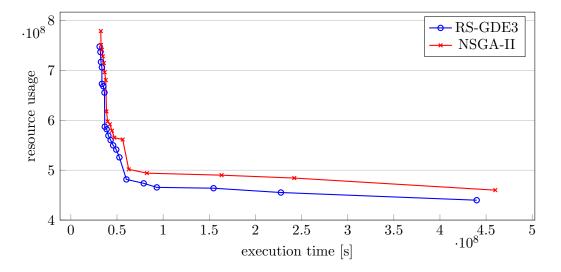

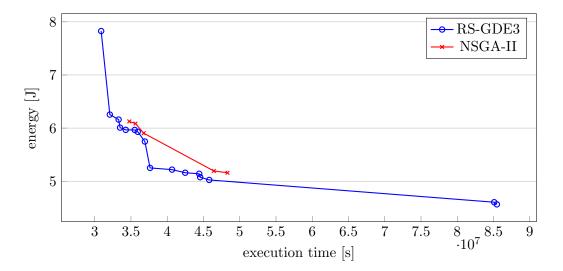

|   | 4.5                                                   | Exper             | imental Results                                                    | 50 |  |  |  |  |

|   |                                                       | 4.5.1             | RS-GDE3 Evaluation                                                 | 50 |  |  |  |  |

|   |                                                       | 4.5.2             | Energy-Time Trade-off as a Function of Resource Usage $\ . \ .$    | 51 |  |  |  |  |

|   |                                                       | 4.5.3             | Impact of Turbo Boost                                              | 56 |  |  |  |  |

|   |                                                       | 4.5.4             | Evaluation of RS-GDE3 for Dual-Objective Optimization $\therefore$ | 59 |  |  |  |  |

|   |                                                       | 4.5.5             | Tiling Effects                                                     | 59 |  |  |  |  |

|   | 4.6                                                   | Summ              | nary                                                               | 61 |  |  |  |  |

| 5 | Significance-driven Optimization of Code Execution 63 |                   |                                                                    |    |  |  |  |  |

|   | 5.1                                                   | Introd            | luction                                                            | 63 |  |  |  |  |

|   | 5.2                                                   | Relate            | ed Work                                                            | 65 |  |  |  |  |

|   | 5.3                                                   | Signifi           | icance                                                             | 66 |  |  |  |  |

|   | 5.4                                                   | Metho             | odology                                                            | 70 |  |  |  |  |

|   |                                                       | 5.4.1             | Fault Model                                                        | 70 |  |  |  |  |

|   |                                                       | 5.4.2             | Energy Savings Through Unreliability                               | 71 |  |  |  |  |

|   |                                                       | 5.4.3             | Experiment Setup                                                   | 72 |  |  |  |  |

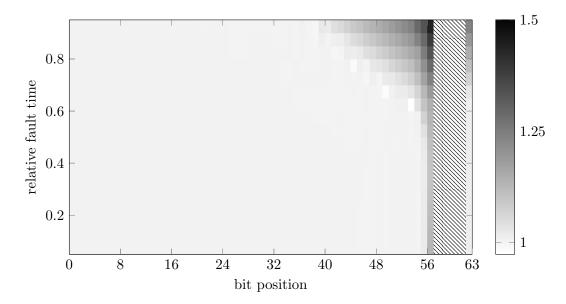

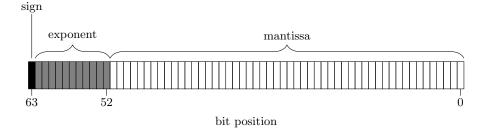

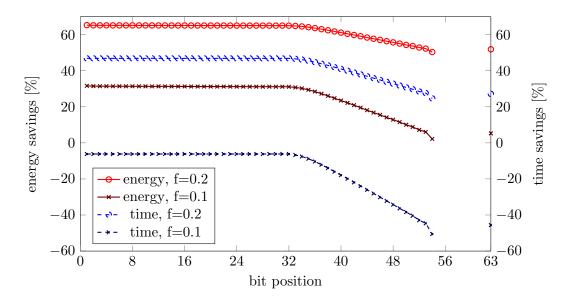

|   |                                                       | 5.4.4             | IEEE 754 Double-precision Floating-point Format                    | 74 |  |  |  |  |

|   | 5.5                                                   | Result            | ts                                                                 | 75 |  |  |  |  |

|               |        | 5.5.1                                      | Sequential Reliable Jacobi                   | 76  |  |  |  |

|---------------|--------|--------------------------------------------|----------------------------------------------|-----|--|--|--|

|               |        | 5.5.2                                      | Parallel Reliable Jacobi                     | 78  |  |  |  |

|               |        | 5.5.3                                      | Significance-dependent Reliability Switching | 79  |  |  |  |

|               | 5.6    | Summ                                       | ary                                          | 82  |  |  |  |

| 6             | Con    | Compiler-assisted Time and Energy Modeling |                                              |     |  |  |  |

|               | 6.1    | Introd                                     | luction                                      | 83  |  |  |  |

|               | 6.2    | Relate                                     | ed Work                                      | 85  |  |  |  |

|               | 6.3    | Model                                      |                                              | 86  |  |  |  |

|               |        | 6.3.1                                      | Method                                       | 86  |  |  |  |

|               |        | 6.3.2                                      | Automatic Region and Parameter Detection     | 87  |  |  |  |

|               |        | 6.3.3                                      | Automatic Parameter Extraction               | 90  |  |  |  |

|               |        | 6.3.4                                      | Execution Time Prediction                    | 90  |  |  |  |

|               |        | 6.3.5                                      | Energy Prediction                            | 97  |  |  |  |

|               | 6.4    | Exper                                      | imental Setup                                | 98  |  |  |  |

|               | 6.5    | Result                                     | зв                                           | 100 |  |  |  |

|               | 6.6    | Summ                                       | ary                                          | 104 |  |  |  |

| 7             | Con    | clusio                                     | n                                            | 105 |  |  |  |

|               | 7.1    | Contri                                     | ibutions                                     | 105 |  |  |  |

|               | 7.2    | Future                                     | e Work                                       | 108 |  |  |  |

| $\mathbf{A}$  | ppen   | dices                                      |                                              | 111 |  |  |  |

| $\mathbf{Li}$ | st of  | Symb                                       | ols                                          | 113 |  |  |  |

| Li            | st of  | Figur                                      | es                                           | 115 |  |  |  |

| Li            | st of  | Table                                      | S                                            | 119 |  |  |  |

| $\mathbf{Li}$ | st of  | Defini                                     | itions                                       | 121 |  |  |  |

| Li            | st of  | Exam                                       | ples                                         | 123 |  |  |  |

| $\mathbf{Li}$ | st of  | Algor                                      | ithms                                        | 125 |  |  |  |

| B             | ibliog | graphy                                     |                                              | 127 |  |  |  |

## Chapter 1

## Introduction

### 1.1 Motivation

Originally, research in the field of hardware design and software engineering mainly targeted high computational performance, the reduction of execution time being the chief concern of processor architects and software developers. However, increasing clock frequencies imposed a limit regarding sequential speed improvement, as processor designs of this era hit a power wall that made any further advances in this direction technically infeasible. This marks an important occurrence of increased non-functional interests in high performance computing, as additional concerns such as power consumption, energy costs and heat dissipation started to pose limiting factors in new hardware designs. Researchers and engineers shifted to multi-core and later many-core computing as the means to further increase performance partly due to these constraints. While this paradigm change toward increased parallelism offers large potential, providing high performance at reduced power, energy and heat expenses, these non-functional concerns are still the main design limitation of today's architectures [48], and consequently also software design and optimization. Also, they opened up new branches of research that tackle previously non-existent problems or exploit new potential. These non-functional concerns, specifically analysis and optimization of energy in addition to execution time, represent the focus of the research presented in this thesis.

The original first-class citizen among non-functional parameters is high performance or short execution time, and it has been targeted by various branches of computer science research since the beginning of high performance computing. The increasing memory gap [139], which is the time delay for a memory access to be completed, has led to memory hierarchies composed of caches. Optimizing their usage gave rise to many fields of research, with examples in the area of source code transformations such as loop tiling [23], optimizing data cache usage, or program repositioning [85], which aims at reducing instruction cache misses. Similar endeavors followed every other new development in hardware design.

However, in the past two decades, also power and energy have become increasingly important entities, evident by a growing amount of literature dating back to the 1990s dealing with power modeling [22] and simulation [9], or energy modeling [108], and also a plethora of optimization techniques addressing power and energy. Although not as long-established as performance optimization, energy and especially power represent the main constraint when designing new hardware. This entailed technologies such as dynamic voltage and frequency scaling (DVFS), one of the most ubiquitous means of providing a trade-off between execution time and power or energy, and more recently Turbo Boost [25]. The importance of power (and also energy in part) has been further aggravated by recent events such as the 20 megawatt power limit [131]. It states that supercomputing centers must not consume more than 20 MW of power in order to be feasible with regard to infrastructure costs. Combined with the strive for exascale computing, a redoubling of efforts is required to achieve these goals.

### 1.2 State of the Art

There is an abundance of related work regarding performance, power, energy, or other non-functional parameters in the field of HPC, investigating instrumentation, measurement, analysis, modeling, and optimization. However, this section will focus on the most recent work directly related to the research presented in this thesis in Chapters 4 to 6. For clarity, only an outline is given here, with more detailed discussions of related work presented in the respective section of the individual chapters.

#### 1.2.1 Multi-objective Auto-Tuning

Despite the rising of new concerns such as power and energy over the past two decades, high performance has always remained among the most important goals of research in HPC hardware and software optimization. In order to address this presence of multiple optimization goals, a lot of related work evaluates their new optimization methods in a multi-objective manner. Examples include hardware design exploration [94], self-tuning libraries for linear algebra [135, 137] or signal processing [42, 100], or application-specific auto-tuning [4, 30].

#### **Open Problems**

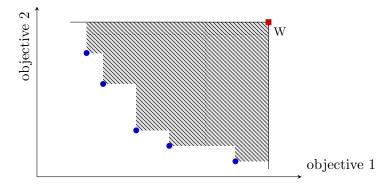

Many works that address multi-objective problems assign fixed weights to these objectives, effectively reducing the problem to a mono-objective one and masking any potential trade-offs between conflicting objectives. The energy-delay-product (EDP) [48] is among the most popular of such fixed-weight functions. While, over time, additional metrics were established that balance the importance of the individual objectives, they fail at capturing the true trade-off between conflicting objectives but rather sample this trade-off at pre-defined points. This results in limited flexibility in case the preference regarding the objectives changes. Hence, very few works apply true multi-objective optimization. Furthermore, there are additional objectives such as resource usage [65] that might need to be considered besides execution time and energy. However, at this time, there are no works in HPC that consider more than two objectives.

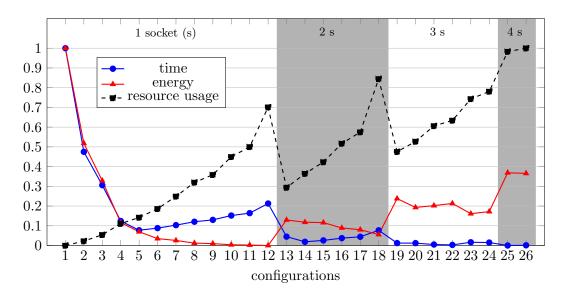

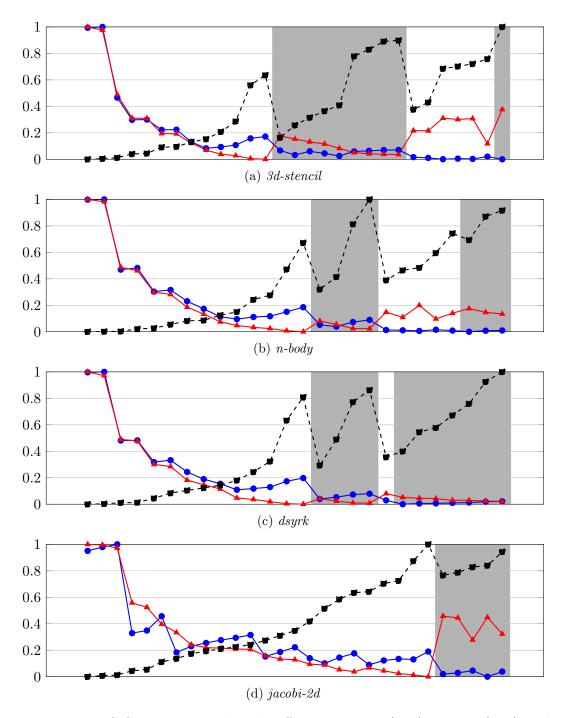

For this reason, we present a true multi-objective auto-tuner in Chapter 4, published in [53], that optimizes parallel programs for three conflicting objectives, execution time, resource usage and energy consumption. Additionally, based on a combined compiler-runtime framework, our method allows for both compile-time parameters (such as source code transformations) and run-time parameters (such as degree of parallelism and DVFS) to be combined in the same optimization process, whereas many works are limited to one of the two. Finally, we obtain generalized guidelines that can aid in tuning parallel programs for these three conflicting objectives.

#### 1.2.2 Significance-driven Optimization of Code Execution

One of the results of the industry's shift towards including energy and power concerns is the development of efficient tools such as DVFS. It provides the means to manage the trade-off between time and power or energy by reducing the frequency and voltage. However, DVFS as deployed throughout most of today's commodity hardware is limited to operating well above the threshold voltage that is required for transistors to function reliably. On the other hand, the concept of near-threshold voltage (NTV) operates hardware closer to this threshold voltage, offering much larger power reductions at the expense of performance. Nevertheless, while NTV has been a topic of interest for some time [69], its entailed higher probabilities of hardware faults have prevented its wide-spread deployment in HPC beyond research projects. However, popular goals such as exascale performance at 20 megawatts might depend on such innovative methods. As a result, the scientific community has studied hardware and software mechanisms that render programs fault-resilient [34, 68, 69, 70]. Also, there is research investigating the effect of faults on software [35] but it ignores the impact of fault recovery on energy or how to leverage fault resilience for energy reduction. Also, very few works deal with partial protection schemes [78].

#### **Open Problems**

Although there is research in both NTV operation and the effect of faults on codes in the context of HPC, few works combine these aspects. Those that do employ protection mechanisms that are explicitly designed to cope with the unreliability of hardware when operated at NTV. Contrary to that, we investigate the effect of this unreliability on unprotected codes in the context of reducing energy consumption in Chapter 5, published in [52]. Specifically, we examine the behavior of iterative solvers that naturally converge to solutions. We aim at reducing overall energy consumption by reducing power via NTV and mitigating the performance impact via parallelism. Moreover, we investigate partial protection mechanisms by evaluating the significance of individual parts of the target program and its data.

#### 1.2.3 Compiler-assisted Execution Time and Energy Modeling

A lot of literature dealing with non-functional parameters investigates their predictive modeling. This is often required by optimization methods that open large parameter search spaces to be explored. For this reason, many works tend to employ predictive models that aid in the navigation of these search spaces. Establishing a basis, there are many analytical works that attempt to model non-functional parameters or their relationships. Prominent examples are the roofline model for execution time [140] and energy [26], Wattch [22] or ECM [115]. Then, a vast number of predictive models is built on top of this basis. These include models requiring user input [18, 113, 117], as well as automatic approaches [19, 55, 77]. While most of them aim at performance prediction, some also target power or energy prediction, and many stochastic approaches support additional non-functional parameters.

#### **Open Problems**

The majority of predictive methods uses run-time information such as performance counters to generate or train their models. Often, a parameter study involving multiple search space samples is required for example to obtain enough support nodes for function fitting. Hence, these methods require multiple target program executions. However, static information can help in this process and reduce the number of samples required for achieving a desired level of accuracy. Few works incorporate static information, nevertheless they still partially rely on stochastic methods that require multiple target program executions [19] or employ the user to provide key information regarding important program parameters. Furthermore, many of the models found in literature are problem-size or machine-size specific and need to be re-trained if these parameters change.

Contrary to these works, in Chapter 6, we investigate a modeling approach based on the capabilities of a compiler that employs a single execution of distributed memory parallel programs for model generation. We show that using a compiler's data flow analysis, we can obtain models parametrized for both problem size and machine topology without depending on user directives. In addition, we show how automatic source code transformations can be used to reduce the overhead of model generation. Finally, we build and evaluate these models for both execution time and energy.

#### **1.3** Organization

This thesis is structured as follows. Chapter 2 introduces a formal model that describes the hardware entities, software entities and their relationship this research is based on. The realization of this formal model in a practical non-functional instrumentation and measurement framework within the Insieme Compiler is described in Chapter 3. Thereafter, Chapters 4 to 6 present some of the research based on this model.

First, Chapter 4 discusses auto-tuning trade-offs of parallel programs between execution time, resource usage, and energy consumption in a multi-objective context using iterative compilation. Second, Chapter 5 introduces the notion of code significance, how it can be attributed to code regions of parallel programs and their data, and investigates whether code significance can drive code execution on unreliable hardware. Third, Chapter 6 shows how compiler knowledge can facilitate the generation of analytical models for execution time and energy prediction and reduce their training overhead. Finally, Chapter 7 provides a conclusion to the research done thus far and lists potential future work to be explored.

## Chapter 2

## Model

In order to model the power, energy and time behavior of hardware and software in the context of today's high performance computing systems and applications, a model regarding their behavior and technical background with respect to the physics involved is required. Section 2.1 will introduce the hardware model on which the remainder of the thesis is based. Subsequently, Section 2.2 will establish the corresponding software model used to represent the programs targeted in this work.

This chapter is based on work on performance and energy benchmarking and analysis, published by under the titles *Performance Analysis and Benchmarking of the Intel SCC*, see [50], and *Modeling CPU Energy Consumption of HPC Applications on the IBM POWER7*, see [51].

## 2.1 Hardware Model

The major non-functional parameters of interest in this work are the execution time and energy consumption of parallel programs. However, they are actually properties of the hardware that executes these programs. For this reason, we require a hardware model. First, we describe the physical relationship between computer hardware, time, power and energy consumption. Second, a hardware topology model is defined that describes the type of hardware components, their connections and semantics. Finally, a list of key properties is established with respect to the goals of this thesis.

#### 2.1.1 Physics Background

In this section, a brief overview of the relationship between time, power and energy is presented within the context of computer hardware. Energy E is defined as the integral of power over time, i.e.

$$E = \int_0^t P_{\text{inst}} \, \mathrm{d}t \tag{2.1}$$

where  $P_{\text{inst}}$  is the instantaneous power. However, for several reasons such as the highly dynamic nature of power and measurement limitations, etc, instantaneous power is usually difficult to work with in practical contexts. Instead, Equation (2.1) is often numerically approximated by using average power  $P_{\text{avg}}$  instead:

$$E = t \cdot P_{\text{avg}} \tag{2.2}$$

For brevity, throughout this thesis, P always denotes  $P_{\text{avg}}$  over a given interval, unless specified otherwise. The majority of today's high performance computing hardware comprises up to billions of transistors [12]. These transistors and their interconnects are the main causers for execution time, power dissipation and hence energy consumption<sup>1</sup>. For any piece of transistor hardware, P can be divided into its static and dynamic component

$$P = P_{\text{static}} + P_{\text{dynamic}} \tag{2.3}$$

where  $P_{\text{static}}$  denotes the static power drawn by the hardware without doing any actual work (e.g. no clock signal, no state changes, etc.) and  $P_{\text{dynamic}}$  denotes the dynamic power drawn by the transistors processing the actual workload. These terms are affected by parameters such as fabrication process size (e.g. 22 nanometers [29]), material choice and quality, supply voltage, temperature, and others, and may differ between multiple samples of the same integrated circuit.

Since  $P_{\text{static}}$  is a static component and not affected by the workload, we focus on  $P_{\text{dynamic}}$ , which can be further broken down into

$$P_{\rm dynamic} = C \cdot V^2 \cdot F \cdot \alpha \tag{2.4}$$

where C is the electrical capacitance (a fixed property for a given component), V is the supply voltage, F is the clock frequency and  $\alpha$  commonly known as the *switching* factor or activity factor [22], with  $0 \leq \alpha \leq 1$ . This switching factor denotes how often transistors switch upon a clock signal, with 0 meaning that transistors never

<sup>&</sup>lt;sup>1</sup>Note that according to the first law of thermodynamics, energy can never be actually destroyed in an isolated system but only converted from one form to another (e.g. electric into thermal). Nevertheless, for brevity, the term "energy consumption" is used synonymously in this thesis to denote the conversion and dissipation of electric energy as waste heat.

switch and 1 meaning they switch at every clock signal. The term  $\alpha$  represents a major impact software has on the power and hence also on the energy consumption of hardware. Normal workloads in high performance computing will cause moderate switching factors, and some works simply assume e.g.  $\alpha = 0.5.[22]$

Equation (2.4) also evidently shows that the clock frequency F only affects the dynamic power consumption linearly, whereas the voltage appears as a power of 2 and hence has quadratic impact on  $P_{\text{dynamic}}$ . However, since higher clock frequencies imply shorter switching times as mentioned above, F and V are tightly coupled to a certain degree and changed in unison to ensure stable operation. Literature sometimes coarsens this to a term of power of 3 and refers to this as the "cube root rule" [14], where the power consumption is a cubic function of the speed of computer hardware.

Transistors work on the well-known basis of changing the current between one pair of terminals by applying voltage or current to another pair of terminals. This is commonly known as switching on or off. To operate, a certain minimum V, commonly referred to as the *threshold voltage* [47] or  $V_{\text{TH}}$ , is required at the controlling terminals for the transistor to switch states reliably within a specific time (dictated by the clock rate F), where shorter switching times require higher threshold voltages for reliable operation. Most of today's computer hardware supports operation at varying levels of F and V, with  $V_{\text{TH}} \ll V$  to ensure stable operation.

#### 2.1.2 Topology

The target hardware architecture for this work are distributed and shared memory parallel computers. This encompasses single-chip many-core systems as well as clusters comprised of a large number of multi-core-based nodes. This section defines a hardware topology model that specifies the types of hardware components, how they are connected, what their semantics are, and establishes several key characteristics and relationships among them. A very brief overview of the model is presented at the beginning, with detailed definitions and examples for actual HPC hardware following in the remainder of this section.

In short, a parallel computer is modeled as a directed graph with its vertices representing hardware components of three types (*functional units*, *caches*, *memory units*), with additional components such as *cores* or *nodes* that are obtained via composition. The edges of the graph denote the physical and logical links between these components. This topology model is then enriched in Section 2.1.3 with *non-functional properties* such as clock frequencies that affects the performance of model components with regard to *time* and *power*, and as a result also *energy*. Additionally,

*domains* are introduced that comprise graph components with combined properties. All parts of this model are focused on the research carried out during the course of this thesis. Hardware details that are omitted have no relevance for this research.

#### Definition 2.1 (Parallel Computer)

Let  $\mathcal{U}$  be a set of vertices that model hardware units or hardware components, and  $\mathcal{L} \subseteq \mathcal{U}^2$  be a set of edges representing unidirectional links among them, where  $l = (u_1, u_2)$  with  $l \in \mathcal{L}$  and  $u_1, u_2 \in \mathcal{U}$  denotes a hardware connection that can transfer instructions or data from  $u_1$  to  $u_2$ . Then a parallel computer is defined as a connected, directed graph  $\mathcal{M} = (\mathcal{U}, \mathcal{L})$ . A hardware component  $u \in \mathcal{U}$  is defined as an instance of any of the following types:

- Functional Unit: performs computations,

- Cache: caches memory locations, or

- Memory Unit: stores program or data.

These types are denoted by  $u_{\text{func}} \in \mathcal{U}_{\text{func}}$ ,  $u_{\text{cache}} \in \mathcal{U}_{\text{cache}}$  and  $u_{\text{mem}} \in \mathcal{U}_{\text{mem}}$  respectively, and it is required that  $\mathcal{U}_{\text{func}} \neq \emptyset$  and  $\mathcal{U}_{\text{mem}} \neq \emptyset$ .

As the remainder of this section will show, the three hardware component types of Definition 2.1 are sufficient for modeling distributed memory and shared memory parallel computers. The edges  $l \in \mathcal{L}$  linking individual components represent both on-chip interconnects and network connections. While *caches* are not required for a purely functional model, we include them explicitly to model their non-functional effects on program execution. The individual components are further defined as follows.

#### Definition 2.2 (Functional Unit)

A functional unit is a hardware component that performs actual computations on a specific type of data. It is always linked to at least one memory unit directly, or transitively via one or more caches. A functional unit fetches input data and instructions from memory units or caches, performs the requested computation, and writes output data back to memory units or caches.

Examples of frequently-occurring data types that functional units operate on are

- integer,

- vectorized integer,

- floating-point, or

#### 2.1. HARDWARE MODEL

• vectorized floating-point.

Non-vectorized functional units operating on integer or floating-point data are commonly referred to as ALU and FPU respectively. Vectorized functional units frequently occur in various HPC architectures (for example the Streaming SIMD Extensions (SSE) [119] in the x86 architecture, the Vector Multimedia Extensions (VMX) and Vector Scalar Extensions (VSX) [20] in the PowerPC architecture, etc.) to hide computation latencies and hence speed up computation throughput.

#### Definition 2.3 (Memory Unit)

A memory unit is a hardware device in which program or data are stored during program execution. A parallel computer may consist of multiple memory units, some or all of which which may share physical address spaces.

A memory unit (most often RAM) is always managed by a memory controller. However since such a controller is always present, the hardware model presented here implicitly includes such a controller for every memory unit and memory controllers are not defined or listed separately.

#### Definition 2.4 (Cache)

A cache is defined as a small but fast portion of memory that mirrors a subset of memory locations of memory units for faster access. Caches can be chained, however the ends of such a chain must be connected to a functional unit and a memory unit, respectively. Caches can either hold both program and data (*unified caches*), or be dedicated to only one of the two (*instruction caches* and *data caches*).

Caches are fast, usually on-chip types of memory providing quick access to data residing in memory units (RAM). There are usually multiple levels of caches present in a system, with lower levels holding less data at the benefit of lower latency. The first level (L1) is also typically split into dedicated instruction and data caches. Caches can be private to or shared among multiple execution units and other caches. In cache-coherent systems, complex protocols and policies are employed to ensure data consistency between multiple cores and CPUs, and these protocols and policies can differ between CPU models.

While these definitions are sufficient for modeling the majority of today's HPC hardware, we define a number of aggregated hardware components that denote commonly-occurring compositions of hardware components in HPC hardware.

#### Definition 2.5 (Core)

A core consists of at least one functional unit and a number of *private caches*  $u_{\text{cache}}^{\text{core}} \in \mathcal{U}_{\text{cache}}^{\text{core}}$  with  $0 \leq |\mathcal{U}_{\text{cache}}^{\text{core}}|$  and  $\mathcal{U}_{\text{cache}}^{\text{core}} \subset \mathcal{U}$ . A cache is *private* if it is linked only to functional units or other private caches of the same core.

#### Definition 2.6 (CPU)

A CPU consists of at least one core, and a number of *shared caches*  $u_{\text{cache}}^{\text{cpu}} \in \mathcal{U}_{\text{cache}}^{\text{cpu}}$  with  $0 \leq |\mathcal{U}_{\text{cache}}^{\text{cpu}}|$  and  $\mathcal{U}_{\text{cache}}^{\text{cpu}} \subset \mathcal{U}$ . A cache is *shared* if it is linked to two or more functional units or caches of different cores.

#### Definition 2.7 (Node)

A node consists of at least one CPU and at least one memory unit.

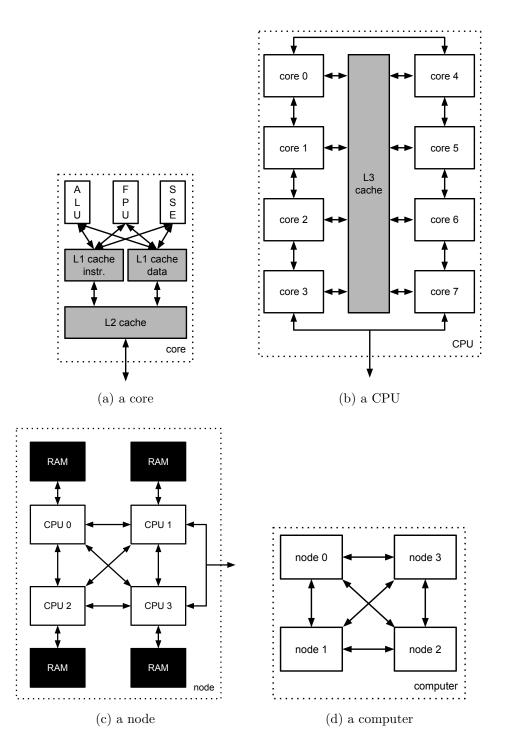

**Example 2.1** (Intel Xeon E5-4650). Figure 2.1 illustrates the usage of aggregated hardware components as per Definitions 2.5 to 2.7, depicting a parallel computer consisting of 4 nodes, each holding 4 Intel Xeon E5-4650 [28] processors or CPUs. Each CPU comprises 8 cores and a shared, unified L3 cache. Every core is equipped with an ALU, an FPU and several functional units operating on vector types (for clarity, only one such vector unit for SEE instructions is shown). Additionally, every core holds a private, unified L2 cache and two private L1 caches, one for instructions and one for data.

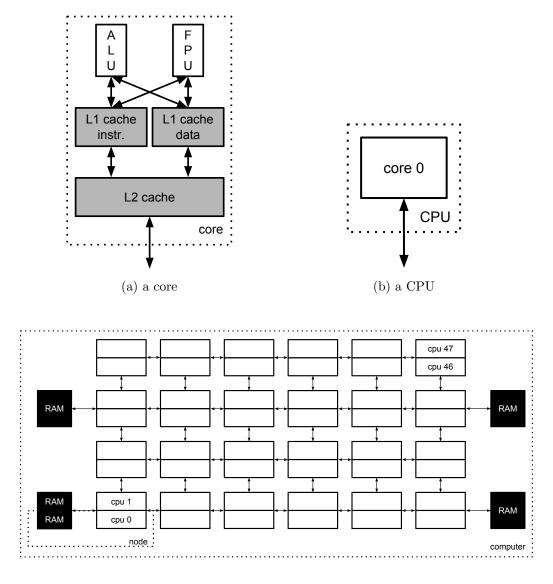

**Example 2.2** (Intel SCC). Similarly, Figure 2.2 illustrates the model representation of the Intel Single-chip Cloud Computer, an experimental prototype with 48 Pentium cores created by Intel Labs [59, 83]. Contrary to most HPC architectures, the individual CPUs of the SCC are connected to their respective memory units via a fast mesh network instead of dedicated memory links and form a distributed memory parallel computer of 48 single-core, single-cpu nodes. The mesh network forwards all data loads/stores between CPUs and memory units, as well as messages passed between the CPUs.

#### 2.1.3 Non-functional Hardware Properties

To reason about the performance or energy consumption of hardware, we need to attribute special properties to every hardware component  $u \in \mathcal{U}$  and links  $l \in \mathcal{L}$ . These properties are the individual terms to compute  $P_{\text{dynamic}}$  of Equation (2.4). We omit C and  $\alpha$  since the former is a fixed physical property, whereas  $\alpha$  is a term

Figure 2.1: Hardware model representation for a parallel computer comprising four nodes each equipped with four Intel Xeon E5-4650 [28] CPUs. For clarity, not all edges are drawn.

(c) a node and the entire SCC

Figure 2.2: Hardware model representation for a single Intel Single-chip Cloud Computer (SCC) [59].

affected by the software that is executed. What remains, are the clock frequency F, which affects both performance and energy of a hardware device, and  $V^2$ , which has direct impact on its energy. However, since they are commonly changed in unison,  $V^2$  also indirectly affects performance.

#### Definition 2.8 (Power Properties)

Let  $\mathcal{M} = (\mathcal{U}, \mathcal{L})$  be a parallel computer. Furthermore, let  $\mathcal{P} \subseteq \mathcal{V} \times \mathcal{F}$  be a set of tuples (v, f), each representing a specific voltage V and a specific clock frequency F as per Equation (2.4). Then there is a  $\mathcal{P}_x \neq \emptyset$  for all  $x \in \mathcal{U} \cup \mathcal{L}$  that denotes valid operational clock frequency and voltage combinations for hardware component x, and every hardware component is always set to work at a specific  $(v_x, f_x)$ . The tuples  $(v, f) \in \mathcal{P}$  are also called *power states*.

**Example 2.3** (Intel SCC). The cores of the Intel SCC support 15 frequency levels that are derived by dividing a base clock frequency of 1600 MHz by divisors 2 through 15. Therefore,  $\mathcal{F} = \{\frac{1600}{i} \in \mathbb{Q} | i \in \mathbb{N} \land 2 \leq i \leq 16\}$ . Furthermore, the SCC cores support 208 voltage levels from 0 V to 1.3 V with a granularity of 6.25 mV. Thus,  $\mathcal{V} = \{i \cdot 6.25 \in \mathbb{Q} | 0 \leq i \leq 208\}$ . Note that while  $\mathcal{V} \times \mathcal{F}$  leads to a total of 3120 possible frequency and voltage combinations, not all of them actually lead to stable system operation. For this reason,  $|\mathcal{P}|$  is usually much less than  $|\mathcal{V} \times \mathcal{F}|$ .

#### Definition 2.9 (Domain)

A domain of a specific non-functional parameter or observable is defined as a set  $\mathcal{D} \subseteq \mathcal{U} \cup \mathcal{L}$  of hardware components and links that are all equally and simultaneously affected. Hence, they represent topological aggregations in a specific non-functional context.

**Example 2.4** (DVFS Domains). *DVFS domains* are an omnipresent example for non-functional parameter domains in HPC hardware. They encompass hardware components for which the voltage or frequency can only be set in unison, or more formally,  $\forall x, y \in \mathcal{D} | (v_x, f_x) = (v_y, f_y)$  for any point in time.

An example of a DVFS domain is present on all Intel Sandy Bridge-EP based CPUs (including the Xeon E5-4650), where  $\mathcal{D}_{VF}$  for a CPU is the set of all cores of this CPU, since all cores adhere to both the same frequency and voltage — in contrast to the Haswell-EP, which supports per-core DVFS settings, leading to multiple  $\mathcal{D}_{DVFS}$  with  $|\mathcal{D}_{DVFS}| = 1$ .

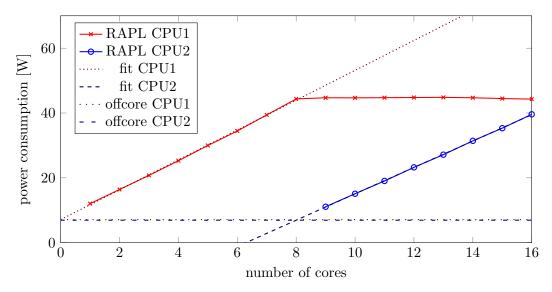

The Intel SCC is an example hardware where frequency and voltage domains are separate domains that do not match. For voltage, cores are grouped into 2x4 clusters, each forming a domain  $\mathcal{D}_{V,i}$  with  $|\mathcal{D}_{V,i}| = 8$  for  $0 \le i \le 5$ . Analogously, for frequency, cores are grouped into 1x2 clusters (also referred to as *tiles*), each representing a domain  $\mathcal{D}_{F,j}$  with  $|\mathcal{D}_{F,i}| = 2$  for  $0 \le j \le 23$ . As a result, the SCC has 6 domains for which the voltage can be set independently, and 24 domains for which the frequency can be set independently. **Example 2.5** (Measurement Domains). A second example for domains are *measurement domains*. These are domains established by non-functional observables, which cannot be measured for individual hardware components. A prominent example is the domain spanned by the Intel Running Average Power Limit (RAPL) interface [31]. It is a hardware feature available on some Intel CPUs starting with the Sandy Bridge generation [31], that offers both the functionality to measure energy consumption and to set power caps that are not to be exceeded by the processor. For the Xeon E5-4650 model, this RAPL interface does not offer energy consumption readings for individual cores but rather all cores, leading to a domain  $\mathcal{D}_{\rm E}$  holding all 8 cores.

#### Definition 2.10 (Time and Power of Computation)

Let  $u_{\text{func}} \in \mathcal{U}_{\text{func}}$  be a functional unit for a specific data type d and f the clock frequency this functional unit operates at. Let furthermore  $(w_i, a_i) \in \mathbb{R}^2$  be a tuple where  $w_i$  denotes the *width* and  $a_i$  the average *instructions per clock* (CPI) of a specific instruction type i operating on data type d. The width  $w_i$ is the number of data type instances instruction i can simultaneously process, with  $0 < w_i$ . The average CPI  $a_i$  is the number of cycles between two processed instructions  $i_x$  and  $i_{x+1}$ .

Then the time it takes  $u_{\text{func}}$  to process i on  $n_d$  instances of type d can be approximated as  $\frac{n_d}{w_i} \cdot \frac{a_i}{f}$ . Similarly, every type of instruction i of width  $w_i$  can be associated with a specific average power consumption  $P_{u_{\text{func}},i,w_i,v,f}$  of  $u_{\text{func}}$  at voltage level v and clock frequency f.

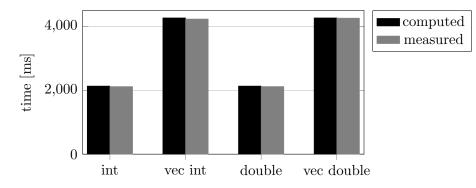

**Example 2.6** (IBM POWER7 Computation Time). The IBM POWER7 CPU [67] holds functional units capable of processing a fused multiply-add (FMA) instruction on integer and floating-point data types in a vectorized and non-vectorized fashion. Figure 2.3a shows the width and CPI information taken from [111]. The CPU was clocked at f = 3.0 GHz, and performed FMA instructions on  $10^{11}$  elements of integer and double-precision floating point types. The CPU can compute 4 elements of integer type and 2 elements of double-precision floating point type per FMA, and requires an average of 0.25 and 0.125 CPI respectively. Setting the variables of Definition 2.10 to these values allows to compute the respective execution times. Figure 2.3b illustrates a comparison with measured values for the same workload.

|                | integer    | double     |

|----------------|------------|------------|

| not vectorized | (1, 0.125) | (1, 0.125) |

| vectorized     | (4, 0.125) | (2, 0.125) |

(a) Width and CPI in the form of (w, a) for fused multiply-add (FMA) instructions of the IBM POWER7 CPU [111].

(b) Computed and measured time for processing 1e11 elements of integer and double precision floating-point type in both vectorized and non-vectorized FMA instructions at a clock frequency of f = 3 GHz.

Figure 2.3: Application of Definition 2.10 for the IBM POWER7 processor [51].

#### Definition 2.11 (Time and Power of Data Transfers)

Let a connected, directed graph  $\mathcal{M} = (\mathcal{U}, \mathcal{L})$  be a parallel computer. Furthermore, let  $\omega : \mathcal{L} \to \mathbb{R}^2$  be a weight function assigning each link  $l \in \mathcal{L}$  a tuple  $(b, a) \in \mathbb{R}^2$  where *b* denotes bandwidth and *a* denotes CPI information. Then  $\mathcal{M}$ can be extended to a *weighted*, connected, directed graph  $\mathcal{G}' = (\mathcal{U}, \mathcal{L}, \omega)$ . Given an amount of data *d* to be transferred from  $u_1$  to  $u_2$ ,  $u_1, u_2 \in \mathcal{U}$  connected via  $l_{u_1,u_2} = (u_1, u_2)$ , then the time of transferring this data from  $u_1$  to  $u_2$  can be computed as  $\frac{d}{b} + a$  where  $(b, a) = \omega(l_{u_1,u_2})$ . Similarly, every link *l* can be associated with a specific average power consumption  $P_{l,v,f}$  when transferring data at voltage level *v* and clock frequency *f*.

**Example 2.7** (SCC Memory and Mesh Network Bandwidth). To show the applicability of Definitions 2.8, 2.9 and 2.11, we compute the average memory throughput of individual cores of the Intel SCC with regard to their physical location as depicted in Figure 2.2c and, therefore, the number of links involved to reach a memory unit. Note that first, the mesh network employs a simple x/y routing scheme, meaning that messages are first routed horizontally and then vertically to reach their destination. Second, the default mapping of memory units to cores follows a symmetrical,

horizontal and vertical bisection of the entire computer into 4 chunks, assigning one memory unit to a set of 12 adjacent cores and ensuring that no node requires more than 4 links to reach a memory unit.

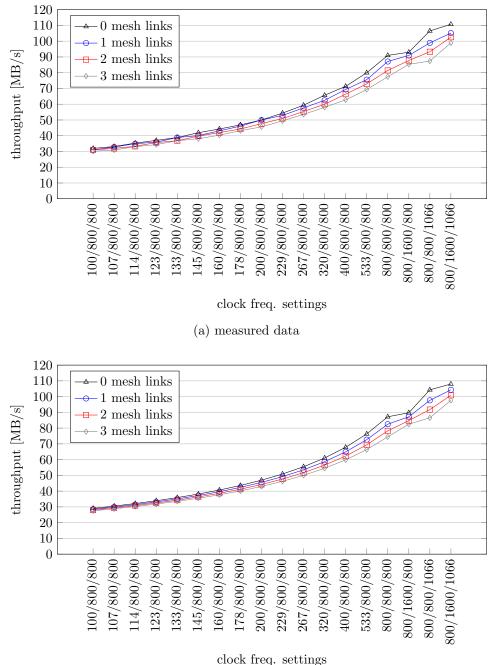

Combining our topology model of the SCC with documented information [74] regarding CPI and bandwidth ((b, a) of Definition 2.11), and clock frequencies ( $\mathcal{F}$  of Definition 2.8), we can compute the maximum expected memory throughput. The bandwidth b is 16 bytes, and the CPI a is given as 40 core clock cycles for a core issuing a read or write request, 4 mesh network link clock cycles to forward a request or data, and 46 memory unit clock cycles for the memory unit to complete the request. Therefore, the overall CPI a of a single memory request and the corresponding answer can be computed as

$$a = \frac{40}{f_{\text{core}}} + \frac{4 \cdot 2 \cdot n}{f_{\text{mesh}}} + \frac{46}{f_{\text{memory}}}$$

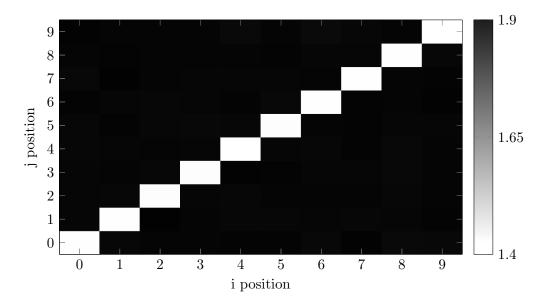

where  $f_{\text{core}}$ ,  $f_{\text{mesh}}$ , and  $f_{\text{memory}}$  denote the clock frequencies of the cores, the mesh network links and the link to the memory unit to complete the request, and n denotes the number of mesh network link hops from source to destination. Figure 2.4 shows the computed and measured memory throughput for  $0 < n \leq 4$  links involved for a set of core, mesh and memory frequencies. The measured data was obtained by running the stream memory benchmark [84] on an actual Intel SCC sample [50, 73].

#### Definition 2.12 (Cache Access)

Let  $u_{\text{func}}$  be a functional unit,  $u_{\text{cache}}$  a cache unit and  $u_{\text{mem}}$  a memory unit connected via links ( $u_{\text{func}}, u_{\text{cache}}$ ), ( $u_{\text{cache}}, u_{\text{func}}$ ), ( $u_{\text{cache}}, u_{\text{mem}}$ ), and ( $u_{\text{mem}}, u_{\text{cache}}$ ). Read requests from  $u_{\text{func}}$  referring to memory locations in  $u_{\text{mem}}$  are first checked by  $u_{\text{cache}}$ , and if it holds a copy of the required memory location, its contents are returned immediately — this is called a *cache hit*. If not, it is a *cache miss*, and the contents are transferred from  $u_{\text{mem}}$  to  $u_{\text{cache}}$  and returned. Cache properties dictate replacement policies (i.e. which data to evict from the cache when loading new data) and whether write requests are cached or not.

(b) computed data

Figure 2.4: Measured and computed memory throughput of the SCC for cores with varying distance from the memory units (0 to 3 mesh network links). The x axis entries represent clock frequency settings in the form of  $(f_{\rm core}/f_{\rm mesh}/f_{\rm memory})$ .

### 2.2 Software Model

This section defines a software model required for discussing and analyzing nonfunctional parameters such as execution time or energy consumption in the context of parallel programs. First, the structure of software is defined, starting with *sequential programs*. They are represented as a graph of *statements* with *control flow edges*. This sequential representation is enriched with *parallel control flow edges* and *communication*, resulting in a *parallel program model*. Second, several properties on this software model are established, such as definitions of *code regions* or non-functional parameters or metrics such as *wall time* or *energy consumption*. The definitions of these metrics are vital due to their frequent use throughout the thesis.

#### 2.2.1 Software Structure

#### Definition 2.13 (Sequential Program)

Let S be a set of vertices denoting program statements and  $\mathcal{E} \subseteq S^2$  be a set of edges between them representing sequential control-flow. Then a sequential program is a directed graph  $\mathcal{A} = (S, \mathcal{E})$ . A control flow edge  $(s_1, s_2) \in \mathcal{E}$  with  $s_1, s_2 \in S$  enforces potential execution of  $s_2$  after  $s_1$ , i.e. if there are two control edges  $(s_1, s_2), (s_1, s_3) \in \mathcal{E}$ , either  $s_2$  or  $s_3$  will be executed after  $s_1$ .

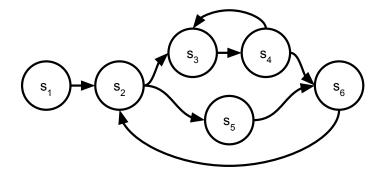

**Example 2.8** (Sequential Program Example). Figure 2.5 shows an example of a sequential program comprising 6 program statements and a number of control flow edges connecting them. Note two back edges,  $(s_4, s_3)$  and  $(s_6, s_2)$ , representing loops.

Figure 2.5: Software model representation of a sequential program.

#### Definition 2.14 (Parallel Program)

Let spawn and merge be new types of program statements expressing parallelism and  $S_p$  be a set of vertices of these types.

Furthermore, let  $\mathcal{E}_p \subseteq \mathcal{S}_p \times \mathcal{S}$  be a set of directed *parallel control flow edges*. For any parallel control flow edge  $(s_1, s_2) \in \mathcal{E}_p$  it is required that either  $s_1$  is of type *spawn* or  $s_2$  is of type *merge*. Contrary to sequential control flow edges defined in Definition 2.13, all parallel control flow edges must be followed, i.e. if there are two parallel control flow edges  $(s_1, s_2), (s_1, s_3) \in \mathcal{E}_p$  then both  $s_2$  and  $s_3$  are executed concurrently after  $s_1$ .

Additionally, let  $\mathcal{E}_c \subseteq \mathcal{S}^2$  be a set of directed *communication edges*. Then  $\mathcal{A}_p = (\mathcal{S} \cup \mathcal{S}_p, \mathcal{E} \cup \mathcal{E}_p, \mathcal{E}_c)$  represents a parallel program. Let  $(s_1, s_2) \in \mathcal{S}$  be a control flow edge and  $[s_2, s_3] \in \mathcal{E}_c$  a communication edge, then  $[s_2, s_3]$  represents data being transferred from  $s_2$  to  $s_3$ , with  $s_3$  being executed after  $s_1$  and completion of the data transfer.

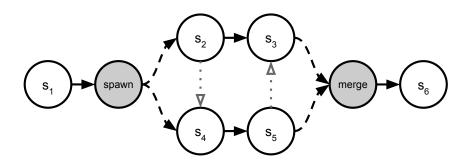

**Example 2.9** (Parallel Program Example). Figure 2.6 illustrates an example of a parallel program consisting of 8 statements, including a *spawn* and a *merge* vertex. There are two edges denoting an increase in parallelism, (spawn,  $s_2$ ) and (spawn,  $s_4$ ), with the semantics of  $s_2$  and  $s_4$  being executed concurrently after *spawn*. Similarly, there are two edges denoting a decrease in parallelism, ( $s_3$ , spawn) and ( $s_5$ , merge), implying that  $s_6$  will execute after  $s_3$  and  $s_5$ . In addition, there are two communication edges shown, [ $s_2$ ,  $s_4$ ] and [ $s_5$ ,  $s_3$ ], denoting the transfer of data from  $s_2$  to  $s_4$  and  $s_5$  to  $s_3$  respectively.

Figure 2.6: Software model representation of a parallel program.

#### Definition 2.15 (Entry and Exit Points)

Every subgraph  $\mathcal{A}' = (\mathcal{S}', \mathcal{E}') \subseteq \mathcal{A} = (\mathcal{S}, \mathcal{E})$  has special sets of vertices

$$\mathcal{E}_e = \{(s, s'_e) \in \mathcal{E} | s \in \mathcal{S} \setminus \mathcal{S}' \land s'_e \in \mathcal{S}'\},\$$

$$\mathcal{S}'_e = \{s' \in \mathcal{S}' | (s, s') \in \mathcal{E}_e \land s \in \mathcal{S}\},\$$

$$\mathcal{E}_x = \{(s'_x, s) \in \mathcal{E} | s \in \mathcal{S} \setminus \mathcal{S}' \land s'_x \in \mathcal{S}'\},\$$

and

$$\mathcal{S}'_x = \{s' \in \mathcal{S}' | (s', s) \in \mathcal{E}_x \land s \in \mathcal{S}\}.$$

Then  $\mathcal{S}'_e$  is called the set of *entry vertices* and  $\mathcal{S}'_x$  is called the set of *exit vertices*. In the case of  $\mathcal{A}' = \mathcal{A}$ ,  $|\mathcal{S}'_e| = 1$ .

#### Definition 2.16 (Sequential Code Region)

A sequential code region is defined as a subgraph  $\mathcal{A}' = (\mathcal{S}', \mathcal{E}') \subseteq \mathcal{A} = (\mathcal{S}, \mathcal{E})$ with exactly one *entry vertex*  $\{s'_e\} = \mathcal{S}'_e$  and exactly one *exit vertex*,  $\{s'_x\} = \mathcal{S}'_x$ . This property is also called *single-entry single-exit*.

#### Definition 2.17 (Parallel Code Region)

A parallel code region is defined as a subgraph  $\mathcal{A}' = (\mathcal{S}', \mathcal{E}') \subseteq \mathcal{A} = (\mathcal{S} \cup \mathcal{S}_p, \mathcal{E} \cup \mathcal{E}_p)$  in which statements can be executed concurrently by different cores (see Definition 2.5).

#### 2.2.2 Non-functional Software Properties

#### Definition 2.18 (Execution and Data Transfer Workloads)

Let S be a set of vertices of a program. Furthermore, let  $n_i$  be the number of instances of instruction type i processed by a hardware unit  $u_{\text{func}}$ . Then each  $s \in S$  can be attributed with  $n_{s,i}$  reflecting the workload s exerts on  $u_{\text{func}}$ . Analogously, let  $n_d$  be the number of instances of data type d processed by hardware unit  $u_{\text{func}}$  and stored in a memory unit  $u_{\text{mem}}$  connected to  $u_{\text{func}}$  (potentially cached by several  $u_{\text{cache}}$  inbetween). Then each  $s \in S$  can be attributed with

#### $n_{s,i}$ reflecting the amount of data that needs to be transferred to $u_{\text{func}}$ .

#### Definition 2.19 (Degree of Parallelism)

Let  $r_i \in \mathcal{R}$  be a parallel code region with  $i \in \mathbb{N}^+$ . Then  $|\mathcal{R}|$  denotes the *degree* of parallelism.

#### Definition 2.20 (Performance Metrics of Code Regions)

Let  $\mathcal{R}$  be a parallel code region, and let  $\tau_{\text{start}}$  and  $\tau_{\text{end}}$  be functions that return the entry and exit times of each  $r \in \mathcal{R}$ . Then the following definitions of metrics can be established:

• *walltime*:

$$t_{\text{wall}} = \max_{r \in \mathcal{R}} (\tau_{\text{end}}(r)) - \min_{r \in \mathcal{R}} (\tau_{\text{start}}(r))$$

• resource usage or cpu time:

$$t_{\text{cpu}} = \sum_{r \in \mathcal{R}} \left( \tau_{\text{end}}(r) - \tau_{\text{start}}(r) \right)$$

• speedup:

$$\sigma = \frac{t_{\text{seq}}}{t_{\text{wall}}}$$

where  $t_{seq}$  denotes the execution time of a sequential code region counterpart of  $\mathcal{R}$

• efficiency:

$$\epsilon = \frac{\sigma}{|\mathcal{R}|}$$

#### Definition 2.21 (Power and Energy Metrics of Code Regions)

Let  $\mathcal{R}$  be a parallel code region and let  $\phi_{x,p}$  be a function that returns the average power consumption of a hardware unit or link  $x \in \mathcal{U} \cup \mathcal{L}$  operating at power state  $p \in \mathcal{P}_x$  when processing a statement  $s \in \mathcal{R}$ . Then the following definitions of metrics can be established:

• average power:

$$P_{x,p,\text{avg}} = \sum_{s \in \mathcal{R}} \left( \frac{\phi_{x,p}(s)}{|\mathcal{R}|} \right)$$

$$P_{\text{avg}} = \sum_{x \in \mathcal{U} \cup \mathcal{L}} P_{x,p,\text{avg}}$$

• energy:

$$E = P_{\text{avg}} \cdot t_{\text{wall}}$$

## 2.3 Summary

In this chapter a hardware and software model were established in order to discuss and analyze non-functional parameters such as execution time or energy consumption in the context of parallel programs. First, the physical relationship between computer hardware, time, power and energy consumption were described. Then, a hardware topology model was defined that describes the type of hardware components, their connections and semantics. Additionally, a list of key properties was established with respect to the goals of this thesis. Subsequently, a software model was defined, describing the structure of target programs within the scope of this thesis. Finally, several vital properties such as code regions and metrics such as wall time and energy consumption were presented.

## Chapter 3

# Insieme Measurement Framework

All work presented in this thesis has been built and integrated in the Insieme compiler and runtime system framework [65], or represents groundwork for it. Hence, the purpose of this chapter is to elaborate on the *instrumentation and measurement* components of Insieme, developed as part of this thesis for the presented work. Nevertheless, this chapter also briefly touches on many of Insieme's other components and capabilities, developed and maintained by the entire Insieme developer team [92], and the use cases of compiling, analyzing and optimizing parallel applications.

The source code for the Insieme compiler and runtime system, including the instrumentation and measurement components described in this chapter, are available online [118].

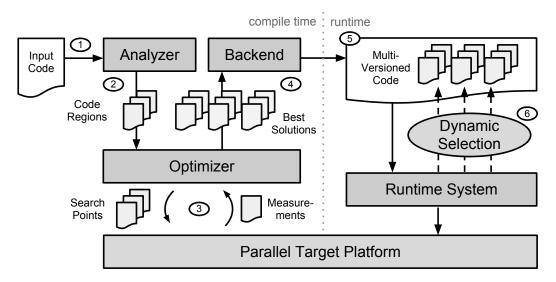

Insieme consists of two tightly integrated main components, namely the *Insieme* compiler and the *Insieme Runtime System (IRS)*. While, in theory, both can be utilized independently, most work —also beyond the scope of this thesis— is carried out by using both in a joint fashion. One main reason for this is their high degree of interoperability by means of transferring information from the compiler to the runtime system and vice versa. Due to the tight integration of both compiler and runtime system, the instrumentation and measurement framework is distributed among both of these components to provide non-functional program information. The compiler is responsible for instrumenting the program, issuing measurements, and retrieving results. The runtime system provides an execution environment for the program and performs the actual low-level measurements, offering non-functional information to the user or compiler for further use. Both of these aspects are addressed individually, first the compiler in Section 3.1 and second the runtime system in Section 3.2.

## 3.1 Compiler Component

This section outlines the compiler component of the measurement framework, focusing on the compiler's view of program *regions*, *metrics* and how the compiler conducts measurements using *executors* and retrieves non-functional run-time data.

## 3.1.1 Overview

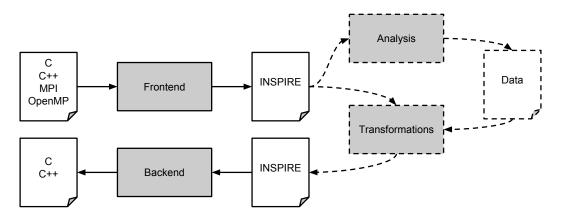

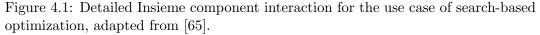

The Insieme compiler comprises multiple components as sketched by Figure 3.1. Source code — be it C or C++, enriched with parallel constructs such as OpenMP pragmas or MPI communication primitives — is parsed by the *frontend* and converted into *INSPIRE* or *IR*, the unified intermediate representation of Insieme [64]. This intermediate representation of the input program allows analyses and transformations to be applied for a large number of use cases ranging from simple code region identification to complex loop transformations [53] or task optimizations [122]. The IR is then read by the *backend*, which again synthesizes C or C++ source code that is to be compiled by a backend compiler such as GCC [39]. It should be noted that Insieme offers multiple backends for code generation, however, only the *runtime backend* generates code that conforms to the application model of the runtime system and using it is mandatory for obtaining measurements with the measurement framework described in this chapter.

The process described above can be seen as a single invocation of the compiler, however all of the aforementioned components are highly modularized and can be applied in many ways (e.g. multiple invocations of the backend with differently transformed IR instances). For this reason, the instrumentation and measurement framework is highly modularized as well, offering a number of individual entities as follows:

- region specification,

- region identification,

- region instrumentation,

- metric specification,

- facilities for compiling and executing instrumented programs to obtain measurements, and

- parsing result data.

These components are described in detail throughout the remainder of this section.

Figure 3.1: Insieme component interaction.

## 3.1.2 Region Specification, Identification and Instrumentation

Code regions from the software model point of view have been defined in Definitions 2.16 and 2.17. Within the compiler, they consist of a pair of INSPIRE statement addresses representing  $s_e$  and  $s_x$ , the entry and exit statements of the code region, as well as a linear index. A single statement address can also be instrumented, in which case  $s_e = s_x$ . Starting and ending a region via  $s_e$  and  $s_x$  is also referred to as *opening* and *closing* a region, and regions are called *open* if their entry statement has been executed but not the exit statement. Regions can be arbitrarily nested as long as an open region is not re-opened, and every exit statement must close the region that was most recently opened.

**Example 3.1** (Compiler Regions). Figure 3.2 illustrates an example of valid code regions within INSPIRE. Both R1 and R2 are cases where  $s_e$  and  $s_x$  refer to the same statement address, in this case a for statement. R3 illustrates the case of  $s_e \neq s_x$ .

| 1 | $for(x = 0N:1) $ {                                      | ן                       |    |

|---|---------------------------------------------------------|-------------------------|----|

| 2 | $\mathbf{for} (\mathbf{y} = 0 \dots \mathbf{M}; 1)  \{$ | )                       |    |

| 3 | counter $+=$ element [y];                               | <b>R</b> 2              |    |

| 4 | }                                                       | J                       | R1 |

| 5 | sum[x] = counter;                                       | <b>)</b> R3             |    |

| 6 | counter $= 0;$                                          | <b>f</b> <sup>110</sup> |    |

| 7 | }                                                       | J                       |    |

Figure 3.2: Example region identification for 3 regions: two loops (R1 and R2) and two assignments (R3).

There are three main ways of identifying code regions to be instrumented by the compiler:

- **Pragmas** The Insieme compiler offers pragmas that direct the compiler to consider the following statement a code region. The syntax for such pragmas is **#pragma insieme region(***id***)** where *id* is the index of the region. The user is required to ensure continuous indices with  $0 \le id < N$  where N is the total number of regions. The same index may appear multiple times for user-defined aggregation, however the user must also ensure that a region is not nested in another with the same index. Also, this method is limited to  $s_e = s_x$ .

- **Analysis** There are a number of utilities available within the compiler to identify code regions that match certain properties. These are called *region selectors*. Examples are specific statements such as **for** or **pfor** loops, function calls with specific signatures, or more complex regions such as covering non-blocking MPI communication and corresponding wait calls, or arbitrary region selection that matches a given size.

- **Program** The Insieme compiler can be instructed to consider the entire program a code region.

Since the actual measurement of non-functional parameters takes place at runtime, any regions of interest must be marked for the runtime system. To that end, the instrumentation framework prepends an Insieme Runtime System directive ir\_inst\_region\_start(id) to every start address  $(s_e)$  and appends the corresponding directive ir\_inst\_region\_end(id) to every end address  $(s_x)$ . These directives instruct the runtime system to perform measurements, as further detailed in Section 3.2.

## 3.1.3 Measurement Framework

The measurement framework is responsible for collecting a list of all metrics requested by the compiler (or the user), compiling the target program, conducting the actual measurement and parsing the measured data.

## Metrics

Metrics are represented by a syntax tree structure, to allow the specification of userdefined metrics based on low-level metrics. Each user-requested metric, such as energy consumption, is denoted by the root node of such a tree, with its children consisting of aggregation operators of low-level metrics that represent the leaves. Low-level metrics can be defined arbitrarily by the user, however each requires an implementation in the runtime system to collect data for it. Available aggregation operators include *addition*, *subtraction*, *multiplication*, *division*, *minimum*, *maximum*, and *average*. Additionally, for convenience, there is a *none* operator for specifying metrics that do not require any aggregation. Example 3.2 show examples of metrics using the *division* operator.

Example 3.2 (Compiler Metric Structure).

$$total\_energy = div(average\_power, wall\_time)$$

(3.1)

$$efficiency = div(div(cpu\_time, wall\_time), num\_workers)$$

(3.2)

When specifying composed metrics for measurement, the compiler automatically resolves their leaves and composes a list of them to be forwarded to the runtime system. While doing so, the list of leaves is checked for special external instrumentation requirements, such as linking external libraries (e.g. the PAPI [88] library for hardware counter information) or ensuring specific system-level register access (e.g. Intel Running Average Power Limit (RAPL) [136, 54, 31]). This minimizes the software footprint and number of system privileges required to conduct measurements.

## Executors

Once the metric leaves and the external instrumentation requirements have been identified, the program is compiled with a backend compiler such as GCC [39]. This binary is then handed to one of Insieme's *executors* along with the metric leaves and external instrumentation requirements. These executors are responsible for managing the program execution, i.e. transfer of the binary if necessary to a remote target system, executing it in a given environment with given program parameters, and transferring measurement result files back to the machine running the compiler. There are several executors available, including

- **local executor** executes the binary on the local system (e.g. the one running the compiler),

- **SSH executor** executes the binary on a remote system via ssh and ensures proper moving of files to and from the remote machine, and

- **MPI executor** executes the binary on a remote system with additional mpi-specific settings such as target hosts, number of ranks, etc. .

When the runtime system executes and measures the program, it creates performance files that hold the results of the respective measurements (see Section 3.2). These performance logs are copied back by the executor if required, and then parsed by the compiler. The compiler then computes the originally requested, composed metrics.

## **3.2 Runtime Component**

This section describes the Insieme Runtime System (IRS), with special attention paid to the *region-based* measurement component. It will elaborate on the specification of *metrics* and *metric groups* within the IRS and shows their importance in providing the means for *user-defined metrics* and *metric aggregation*.

## 3.2.1 Overview

The IRS [121] provides a shared memory parallel application model environment that implements INSPIRE semantics. It can execute INSPIRE programs that were synthesized by the *runtime backend* of the Insieme compiler. In order to adhere to the IRS application model, programs or program parts are encoded into *work items* which represent schedulable entities. These work items are executed by *workers*, which represent software threads that are user-managed from the perspective of the operating system. Workers form *work groups* that allow limiting synchronization in parallel contexts.

The IRS is implemented in C99 with selected component parts written in low-level assembler for more direct control and reduction of overhead (e.g. hardware timestamp retrieval or context switches). The workers are implemented using pthreads [89], however an abstraction layer allows the usage of alternative threading libraries such as Windows threads [138]. These abstraction layers also allow providing alternative implementations with respect to different instruction set architectures such as x86 or PowerPC.

## 3.2.2 Measurement Framework

There are two independent components in the IRS that provide measurement features:

**region-based** This component is used for measuring code regions that were identified and marked by the compiler or the user. It is capable of measuring non-functional data for both sequential and parallel regions identified via the directives ir\_inst\_region\_start(id) and ir\_inst\_region\_end(id) as described in Section 3.1.2.

event-based This component is mostly used for functional and performance debugging of the IRS itself. It can record the time and origin of several types of events, such as a work item starting execution, a worker going to sleep due to a lack of work, or a work group completing a barrier.

Since the region-based component is much more often used in non-functional analysis and optimization than the event-based one, this section will further detail on the features and characteristics of the former.

The region-based instrumentation and measurement component of the IRS is designed to provide low-overhead data collection from a wide range of sources such as external libraries or hardware registers. To that end, the data collection within the IRS is centered around two main entities: *metrics* and *metric groups*. The former represents individual metrics such as *wall time* or *energy consumption*, while the latter represents a grouping of metrics that share common instrumentation or measurement code, usually because they are obtained from the same source (e.g. the same external library). The specifications of metrics and metric groups are subsequently described, with an illustration of their usage following in Algorithm 3.1.

#### Metrics

Contrary to the compiler, the IRS does not require the compiler's tree structure for representing metrics, since it only measures the metric leaves of this tree structure. For this reason, the IRS instead holds a list of metrics, all adhering to a common, generic specification. This generic specification allows new metrics to be implemented solely by providing their specification, and removes the need for modifications in components of the IRS other than the measurement component. The specification for metrics includes the following items:

name The name of the metric.

type The data type of the metric.